در حال حاضر محصولی در سبد خرید شما وجود ندارد.

طراحی منطق با Vitis-HLS

عنوان اصلی : High-Level Synthesis for FPGA, Part 2 - Sequential Circuits

سرفصل های دوره :

پرولوگ:

معرفی

ساختار دوره

HW / SW Setup:

vivado-hlx

vivado و vitis-hls

نصب Vivado HLX

نصب تست

d flip-flop (DFF):

معرفی

مدار متوالی

سیگنال ساعت

مفهوم دولت

سیگنال بازنشانی

ثبت نام

DFF Lab01

DFF Lab02

تمرینات

جریان طراحی تک چرخه:

معرفی

تعریف و ایده

موازی به سریال

سریال به موازی

جریان طراحی IP-Centric

آزمایشگاه موازی موازی موازی

تمرینات

testbench 01:

معرفی

تعریف

موازی با Testbench سریال

سریال به Testbench موازی

شکل موج ورودی

تمرینات

دستگاه دولتی:

معرفی

تعریف

مفاهیم

الگو

ترکیبی از قفل ویتیلز

Commandock-Vivado

تمرینات

نرم افزار:

معرفی

تایمر

debouncer

شمارنده

Generator Clock

ژنراتور پالس

پالس های معمولی تک چرخه

Edge آشکارساز

تمرینات

دستگاه تلوانگو:

معرفی

تعریف

Vitis-HLS

vivado

تمرینات

تجزیه و تحلیل منطق یکپارچه (ILA):

معرفی

تعریف

vivado

تمرینات

pipelining function:

معرفی

تعریف

طراحی چند چرخه

طراحی خط لوله

Metrics Performance

مثال IIR

تمرینات

هفت بخش:

معرفی

تعریف

درایور 7SEMENT

7SEGMENT HLS

7segment vivado

چهار رقمی شمارنده

تمرینات

pmod:

معرفی

تعریف

PMOD LED صفحه کلید PMOD

تمرینات

سنتز رابط:

معرفی

Scii Proc & Cons

تعریف

سنتز رابط

سطح بلوک AP_CTRL_HS

سطح بلوک AP_CTRL_HS: Vitis-HLS

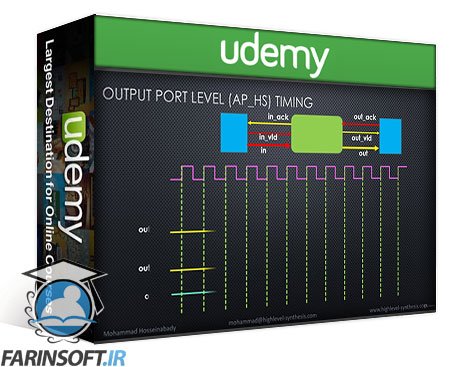

Port Level AP_VLD

Port Level AP_ACK

Port Level AP_HS

تمرینات

پروژه 1: تاس دیجیتال:

معرفی

تعریف

بر اساس شمارنده

lfsr

تمرینات

پروژه 2: UART:

معرفی

تعریف

ساختار طراحی و HLS

فرستنده-vitishls + vivado

Receiver-Vitishls + Vivado

تمرینات

پروژه 3: موتور پله:

معرفی

تعریف

یک فاز: Vitis-HLS

دو فاز: Vitis-HLS

دو فاز با کنترل: Vitis-HLS

یک و دو مرحلهای (نیمه گام): Vitis-HLS

تمرینات

High-Level Synthesis for FPGA, Part 2 - Sequential Circuits

در این روش نیاز به افزودن محصول به سبد خرید و تکمیل اطلاعات نیست و شما پس از وارد کردن ایمیل خود و طی کردن مراحل پرداخت لینک های دریافت محصولات را در ایمیل خود دریافت خواهید کرد.